Substrates Researchers Use to Fabricate Photonic Devices

A postdoc research fellow at

Microphotonics lab requested a quote for the following:

We are looking for some SOI wafers, GaN epitaxial wafers and SiC epitaxial wafers for fabrication of photonics devices (for example: wire photonic

waveguide). So the thickness of the device layer should be around 300 nm. Do you have these kind of wafers in stock?

For the SOI wafers, the thickness devices layer of silicon should be about 250 nm and the silica layer is about 1 micron.

For the SiC and GaN epi wafers, the thickness of the device layer should be about 300 nm.

We don't care much about other properties.

Please reference #121483 for specs and pricing.

Get Your Quote FAST! Or, Buy Online and Start Researching Today!

Silicon Wafers to Fabricate Photonic Devices

A PhD candidate requested help with the following research project:

I would like purchase some Si wafers for substrates. I will be using the substrates to make patterned templates using lithography. Dopant type doesn't matter, I think p- or n- doping levels should

Item number UW2P100 should be sufficient. Just out of curiosity, what is the difference between prime and test. I am just making templates with the silicon wafer to make photonic devices, so conductivity is not important. Will all of the test grade wafers etch at the same rate with a reactive Ion etch tool? Or will there be more process variation since this wafers are of lower quality? If everything is reproducible wafer by waver, then this grade will be sufficient for my applications.

Reference #128336 for specs and pricing.

SiO2 Substrates Used to Fabricate Photonic Devices

A Ph.D. researcher requested a quote for the following:

I am going to order some SiO2

wafers from University Wafer for my photonic research, but I am a

bit confused about the different names of very similar things.

Could you let me know the major

differences between the following items listed on your website:

Most

importantly, which wafer offers

the best surface flatness, and which one has the best purity?

I will order about 10 wafers at the beginning, and will continue to purchase on regular basis if the wafers fit well with my research.

Wafers should be 4 inch, double side polished, transparent to visible light, and the most important parameters are surface flatness and purity. The wafers will be used for the fabrication of nano-photonic devices.

Thank you.

Reference #144363 for specs and pricing.

Thick Thermal Oxide Silicon Wafers to Fabricate Photonic Devices

A university professor requested help with the following research project:

We need a a quotation for the 15 um thermal oxide on 8'' Si Wafers and we were waiting for a quote for 10 such wafers and 100 such wafers.

We are using them as the substrate to fabricate photonic devices. Due to the specs of the devices we require extremely low loss and thus significant dielectric thickness.

We quoted:

200mm, P type, Boron, <100> ON, 1-30 ohm cm, 725um +/-25, TTV

<10um, Notch, Prime

60,000 ű5% Wet Thermal Oxide on both sides

Reference #222834 for specs and pricing.

Silicon Nitride Substrates to Build Waveguides

A process engineer requested the following quote:

We would like to know if you can provide us with 100 mm <100> Si wafers with 5 microns of thermal oxide and 300 nm of LPCVD SiN on top of it.

We would like to know the quote for 25 wafers, including freight cost and delivery time.

SSP is good enough, and the nitride quality should be the better available with a reasonable price as we are going to use the wafers to build waveguides and other photonic devices.

Please reference #225367.

Fabricating Low-Loss Photonic Devices

A Phd candidate requested a quote for the following:

We are going to purchase some SOI wafers for fabricating low-loss photonic devices. The following spec. are preferred: device layer 220 nm, insulation layer 2-3 um, and standard handling layer (but as thin as possible, 350 um is best). We appreciate it if small square pieces are available, for example, 1 inch x 1 inch. Let's try to quote 25 pcs first. By the way, I am not clear if the optical loss will significantly increase if the device layer is doped with P/B. Please also advise, thanks!

Please refernce #267056 for specs and pricing.

Si3N4 on Fused Silica Used for Photonic Devices

A biomedical graduate student requested the following quote:

We are wondering if you could deposit 100nm Si3N4 on a 4” glass (fused silica) wafer? We will use the nitride for photonic devices, so we need high refractive index and low loss nitride. Would it be possible to use the below recipe to get silicon-rich silicon nitride that we found on your website: The silicon-rich silicon nitride composition can be adjusted to maximize the refractive index and minimize wavelength absorption (908b). By changing the concentration of silicon, nitrogen and hydrogen (see e.g.), the wavelength of the absorption for the 1.9 nm and 2.830 nm waveguides can be adjusted from 3.2 to 2.830 nm.

Reference # 270635 for specs and pricing.

Silicon on Sapphire (SoS) to Fabricate Photonic Devices

A PhD candidate requested the following quote for their research.

I am a PhD candidate looking to purchase silicon-on-sapphire wafers for use in photonic device fabrication. We are looking for a silicon layer grown on a sapphire substrate, with silicon thickness near 600nm. We have some flexibility in Si thickness: if Si is thicker than 600nm, (e.g., a few micron) we can easily etch it down to our target. Could you please provide a quote for 4" silicon-on-sapphire wafers with silicon film thickness >=0.6um? Could I also get a quote for the SoS wafers as described, pre-cut into 10mm x 10mm diced pieces?

Reference #276252 fpr specs and pricing.

What Are Photonic Devices?

Photonic devices are components that create, detect, manipulate or control light. These can include laser diodes, LEDs, solar and photovoltaic cells, displays and optical amplifiers.

These technologies are used in a variety of applications, from telecommunications to lighting to medical technology. The scientific investigation of these components is important in order to understand how light is emitted, transmitted, amplified, detected and modulated.

A quantum device researcher requested the following:

I am looking for some SOI wafers for fabricating photonic devices. This means the device layer has to be thin, (ideally 300-500nm). It also has to be extremely consistent in its thickness and also smooth. Soitec to a photonics wafer, it is this kind of spec i'm after. A box layer of 1-2 um is fine.

Reference #145606 for specs and pricing.

Fabricating SOI Passive Device

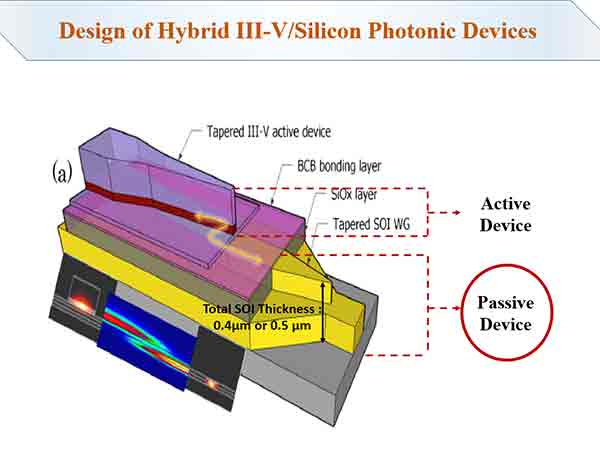

A master student from a photonics research lab requested help with the followin specs:

In my laboratory, we have the research project about SOI Photonic Device. So, we are looking for the company/laboratory that could fabricate our SOI device with the thickness of 0.5 um (the picture as attached).

Could the university wafers help us in fabricating our SOI Passive device.

I have checked them, and I think that SOI with ID 1811 is suitable for us, but the SOI thickness is only 220 nm. We just wondering that too thin for our research, because we will use SOI rib waveguide with the total thickness is around 400 nm or 500 nm (the detail design as attached file).

For the future project, we also want to add the grating (pitch grating around 254 nm) in the SOI rib waveguide.

So, is it possible if we will order with the grating layer in the SOI waveguide?

The second question is could the university wafer also build the SOI active layer? or is it special only for SOI passive layer?

We would like to ask you and the team that if we want to order around 20 chips of the SOI wafers with the special condition (using Silicon RIB Waveguide, with the total thickness of 500 nm, as file attached), So, could you give us the price and time estimation for that devices? Because SOI device is our focus project for currently.

Reference #237913 for specs and pricing.

Silicon Wafer

Silicon is a semiconductor material that is used to manufacture many of the electronics we use in our everyday lives. In addition to computer chips, silicon is also used in many other applications, including sensors and solar cells.

When the crystalline structure of silicon is etched into the form of a wafer, it can take on dopants that make it conduct electricity better. Several different dopants, such as nitrogen, indium, aluminum, gallium, and boron, can be added during the growing process to change its properties, allowing it to become an efficient electrical conductor.

During the growth process, silicon is oriented in one of several relative directions known as crystal orientations, which are typically <111> or <100> (see Figure 5). When cutting the silicon into wafers, the crystal surface is aligned in these same directions. These crystal orientations are critical to many of the electronic and physical properties of a single crystal, as well as to the depth at which ions can be injected into the crystal during ion implantation.

The resulting wafer is cut into manageable sizes using a saw called a “wafer saw.” It then undergoes machining and chemical etching to create the final product. This process is done to minimize damage to the silicon, improve flatness, and reduce bow and warp defects.

After the wafers are sliced into shapes, they are ground to a rough size diameter that is slightly larger than the target diameter of the finished silicon wafer. This allows the diamond edge saw to slice the silicon wafers in a consistent manner. It is important to note that these rough sized wafers are still much thicker than the target specification, which helps to minimize damage to the wafer and thickness variation.

Once the wafers have been sliced, they are then bonded together with an insulating oxide layer between them, which is used as a sacrificial layer for removing oxidized silicon and forming the topmost silicon layer. This method is called Silicon on Insulator (SOI) and is commonly used to build sensing elements and IC devices.

Silicon-On-Insulator (SOI) wafers are used to fabricate high-performance photonic devices. They consist of a thin layer of silicon sandwiched between two insulating oxide layers. These insulating oxides, called upper and under claddings, provide strong optical confinement for the device. This enables the implementation of sub-micrometer-wide optical waveguides, which can be used to send and receive signals at optical frequencies.

SOI technology is the foundation of a new class of semiconductor devices called photonic integrated circuits, which are gaining increased attention in the industry for their scalability, cost-effectiveness and large bandwidth capabilities. They are rapidly being adopted in optical datacom, sensing, biomedical, automotive, astronomy, aerospace, AR/VR and AI applications, and they have the potential to open up new opportunities for the electronics industry.

In addition, SOI technologies offer significant performance benefits compared to bulk technology in the form of lower parasitic capacitance between source and drain and more efficient body biasing, which results in breakthrough dynamic control of transistor switching. SOI technologies also enable the integration of advanced materials, including WSi2 and silicide layers for improved noise reduction in RF and mixed-signal applications.

Photodetectors grown on SOI-based platforms can be characterized by their responsivity, low dark current and wide wavelength band, which are critical requirements for optical applications such as high-speed data communications, quantum information processing, and time-energy entanglement. They are particularly promising in the optical communication market because they can operate at room temperature and can be used for transmission over existing fiber infrastructures.

Another key benefit of SOI technologies is the capability to electrically isolate devices. Unlike conventional pn junction isolation, which causes parasitic devices to create vertical and horizontal cross-talk between devices in the IC, SOI uses a layer of insulating oxide that prevents interference between devices. This is particularly important when designing waveguides and resonators.

A recent example of this is the development of a dual-waveguide directional coupler on SOI, which consists of patterned grating structures inside pre-defined trenches on the bottom and top crystalline silicon layers. The resulting structure is compatible with a range of photonic-based devices, such as lasers, modulators, and filters.

Silicon on Insulator Substrates

Silicon on insulator (SOI) technology combines the high performance of conventional silicon substrates with the full dielectric isolation and low parasitic capacitance of a thin insulating layer. SOI devices are used in a variety of applications including power management, RF electronics, microwave and optical communication.

The insulator material used in SOI devices depends on the application, with sapphire most often being used in high-performance RF and radiation-sensitive applications. SiO2 is often used in microelectronics, as it reduces short channel effects in transistors and other devices.

SOI technology is a highly versatile and customizable process that can be tailored to meet the needs of specific industries. It is especially well-suited for CMOS equipment, making it ideal for high-volume fabrication of photonic devices and circuits.

Okmetic's SOI wafer technology enables a variety of applications, from RF FEM to MEMS and power products, to optical communication and image sensing. These products include RF FEM IC's and lateral HV devices for a variety of power management applications as well as active pixel imaging sensors using a pinned photodiode.

The SOI wafer manufacturing process involves bonding two insulated silicon wafers together leaving an insulating oxide layer between them. The top device wafer can be used for building a sensor element or IC, while the bottom handle wafer is used as a support.

To prepare the SOI wafer, the two silicon substrates are masked in accordance with STI technology (Simulation Technology Integration). The top device layer is deposited, and an insulating pedestal oxide is deposited over the top of it. Then, a stop material is deposited over the pedestal oxide. Then, holes and trenches are etched from the masked regions.

In addition, a Germanium or SiGe alloy layer is grown epitaxially on the device layers to a thickness of between 1 and 50 nm. In this way, a compliant SiGe-Si interface is formed. This interface offers a potential to integrate defect-free alternative semiconductor structures on Si, e.g., Ge nanoclusters on silicon islands in an SOI heterosystem.

Devices

Photonic devices are a wide range of components used to create, manipulate or detect light. These include laser diodes, light-emitting diodes, solar and photovoltaic cells, displays and optical amplifiers.

The main advantage of photonics is that it allows transmission of information at near-light speed, enabling ultrafast communication and other applications such as quantum computing. The ability to transfer data over very long distances is another key benefit of photonics.

There are many types of photonics device structures, based on different fabrication methods. The most common are the carrier injection modulator structure ((106)), the carrier accumulation structure, and the grating coupler structure.

These structures can be fabricated using equipment developed for the CMOS electronics industry, allowing for high volume production with low cost and high yield. However, in some cases, the inclusion of materials in devices that would contaminate CMOS process equipment is necessary, such as the addition of III-V materials for light sources ((109)).

Grating couplers are formed by performing a periodic partial etch into the top surface of the silicon waveguide. They are typically more tolerant to alignment error than carrier injection and accumulation structures, although they can be more difficult to fabricate.

Carriers are injected into the end facet of the waveguide using a laser, which can be adapted for different wavelengths. The laser is usually cooled to about a few thousand degrees centigrade before being applied, reducing the chance of thermal damage to the silicon device. The laser is then positioned within the on-chip waveguide.

Then, the grating is bent around the on-chip waveguide to direct light from one side of the chip to the other, enabling efficient coupling between the on-chip waveguide and an external source or fiber. The bend radius must be large enough to avoid excessive loss due to radiation, but small enough to allow compact integration.

A typical grating bend radius is around 2 mm. The grating is then mounted to the on-chip waveguide using an adhesive. This method is often more convenient and less expensive than the traditional dicing approach, but it requires special equipment and clean room fabrication facilities.