Substrate Used to Develop ASIC

A mechanical engineer requested a quote for the following.

We are planning to develop an ASIC which acts as an interface between MCU and OBD-II inside the vehicle.

Actually this is a new version chip which have some upgrades, 10 years ago we did a similar chip, as technology going advance, we need to add more communication BUS inside the chip, like DoIP and CANFD.

- The questions from me are:

Are you only sell original wafers?

- Can you help me find a Fab who has BCD technique?

Key devices:

High voltage DMOS, negative voltage device, thick gate oxide voltage compliance.

=>

- 5V or 3.3V CMOS

- 36V DMOS (Highside and Lowside)

- The isolation can take -12V

- High sheet rho poly

- Capacitors

Reference #259086 for specs and pricing.

Get Your Quote FAST! Or, Buy Online and Start Researching Today!

SPAD Sensor Array ASIC

A VP Engineering and R&D requested a quote for the following:

Question:

What wafer specs do you recomend be used as a die spacer

with the package?

Answer:

We suggest using: We suggest using:

Silicon Wafer Item #3650 - 200mm P/B <100> 1-100 ohm-cm 725um SSP Prime

Reference #ONL44514 for more specs and pricing.

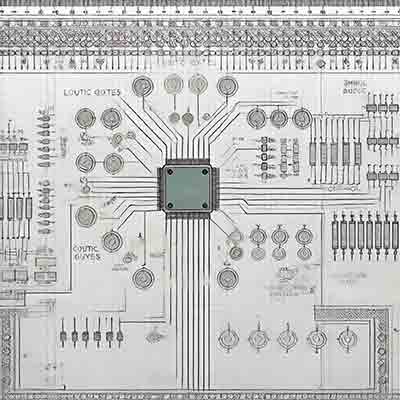

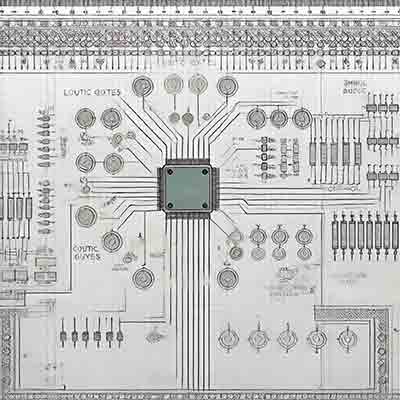

What is Application-Specific Integrated Circuit (ASIC) Design?

ASIC (Application-Specific Integrated Circuit) design is the process of creating an integrated circuit (IC) customized for a specific application or function. Unlike general-purpose ICs, which are designed for a wide range of applications, ASICs are designed to perform a specific task efficiently.

The ASIC design process typically involves several steps:

- Specification: Define the requirements and functions that the ASIC must perform.

- Design Entry: Create the design using hardware description languages (HDLs) like VHDL or Verilog.

- Synthesis: Translate the HDL code into a gate-level netlist using synthesis tools.

- Simulation and Verification: Verify that the design works correctly through simulation and formal verification.

- Physical Design: Convert the netlist into a layout, which involves placement and routing of circuit components.

- Fabrication: Send the layout to a semiconductor foundry to manufacture the chip.

- Testing: Test the manufactured ASIC for functional correctness and performance.

ASICs are widely used in various fields, including consumer electronics, automotive, telecommunications, and medical devices, as they offer better performance, lower power consumption, and reduced cost when produced in high volumes.

What Is the Most Common Silicon Wafer Spec Used in Communications ASIC?

A post doctoreal researcher requested help finding the correct silicon wafer spec for their ASIC project.

Question:

Do you happen to know what is the most typical silicon wafer used in Communication ASICs?

Answer:

For communication ASICs, the most typical silicon wafers used are:

-

Diameter: 8-inch (200 mm) or 12-inch (300 mm) wafers. Larger wafers are preferred for modern processes because they allow more chips to be produced per wafer, which reduces cost.

-

Crystal Ori: The silicon crystal Orientation is usually [1,0,0]. This orientation offers good planar properties and is standard for most CMOS (Complementary Metal-Oxide-Semiconductor) processes, which are commonly used in ASICs for communication.

-

Doping Type: P-type silicon is often used because of its compatibility with standard CMOS processes. However, the choice of P-type or N-type may depend on the specific requirements of the ASIC design.

-

Resistivity: Typical resistivity ranges from 1-10 ohm-cm, depending on the application and the required electrical characteristics.

-

Thickness: The wafer thickness usually ranges from 725 µm for 200 mm wafers to about 775 µm for 300 mm wafers, though this can vary depending on the fabrication process and technology node.

Communication ASICs often use advanced technology nodes (e.g., 7 nm, 14 nm, 28 nm) that require high-quality, defect-free silicon wafers to ensure the performance and reliability of high-frequency circuits.

Reference #237890 for specs and pricing.