We need 500 nanometer low stress nitride on silicon wafers to build resonators and waveguides on Item #3455.

Low Stress Silicon Nitride in Stock and Ready to Ship

Low Stress Nitride on Silicon Wafers For Resonator and Waveguide Fabrication

An applied physics graduate student requested a quote for the following:

Reference #275637 for specs and pricing.

Get Your Silicon Wafer Quote FAST! Or, Buy Online and Start Researching Today!

Silicon Nitride on Insulator Waveguides

A PhD student requested a quote for the following:

I am interested in purchasing your 5um thermal oxide on Si wafers for development of silicon nitride on insulator waveguides (ID 3589). What is the surface roughness for the oxide? What would be the lead time to have these deposited with LPCVD low stress nitride?

Reference #292328 for specs and pricing.

Low Stress Nitride on Silicon Applications

processes, offering high etch selectivity and durability. Surface Acoustic Wave (SAW) Devices:

Low-stress silicon nitride films are used in the construction of SAW devices, which are used in filters and oscillators for communication systems.

Gas Barrier Layers:

Due to its excellent barrier properties, silicon nitride is used as a gas barrier layer in various packaging applications, especially in flexible electronics and displays.

Piezoelectric Devices:

In combination with piezoelectric materials, low-stress silicon nitride can be used in the fabrication of piezoelectric devices for sensors and actuators. Solar Cells:

Used as an anti-reflection coating and passivation layer in silicon solar cells to enhance efficiency by reducing surface recombination and reflecting less light.

Protective Coatings:

Silicon nitride films are applied as protective coatings on various components to enhance wear resistance and chemical stability.

These applications benefit from the unique combination of mechanical strength, thermal stability, chemical resistance, and electrical insulation properties provided by low-stress silicon nitride films on silicon substrates.

processes, offering high etch selectivity and durability. Surface Acoustic Wave (SAW) Devices:

Low-stress silicon nitride films are used in the construction of SAW devices, which are used in filters and oscillators for communication systems.

Gas Barrier Layers:

Due to its excellent barrier properties, silicon nitride is used as a gas barrier layer in various packaging applications, especially in flexible electronics and displays.

Piezoelectric Devices:

In combination with piezoelectric materials, low-stress silicon nitride can be used in the fabrication of piezoelectric devices for sensors and actuators. Solar Cells:

Used as an anti-reflection coating and passivation layer in silicon solar cells to enhance efficiency by reducing surface recombination and reflecting less light.

Protective Coatings:

Silicon nitride films are applied as protective coatings on various components to enhance wear resistance and chemical stability.

These applications benefit from the unique combination of mechanical strength, thermal stability, chemical resistance, and electrical insulation properties provided by low-stress silicon nitride films on silicon substrates.

How are Low-Stress Nitride On Silicon Wafers Made

This paper focuses on the use of low-voltage films to produce high-quality silicon films with low thermal conductivity and high thermal stability, and the application of this material in a variety of applications such as high-performance electronics, photovoltaics, biofuels, solar cells, etc. in a variety of materials and applications. It investigates a number of different approaches to the development of silicon film films and to the reduction of residual stresses described in the publication, with a focus on a series of experiments in the development, production and testing of new silicon nanowires and nanostructures for use in high-quality semiconductors, biofluorocarbons and other materials. [Sources: 1, 3]

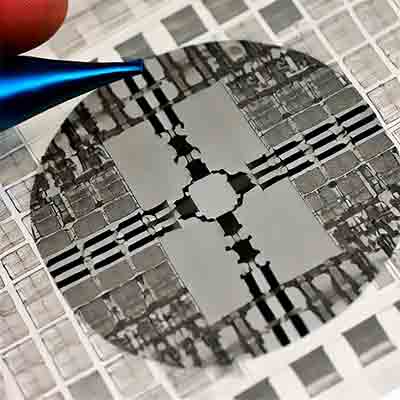

The figure shows the residual stress caused by residual stress on the nickel layer of a low-tension silicon nitride film on a thin silicon wafer. It shows chipping of the thin silicon N-SiN film depending on the nickel thickness. The figure shows the load - induced residual stresses on nickel layers in a silicon film. [Sources: 6]

The specimen observed in this area was produced by etching a window onto a silicon wafer substrate, leaving a thin layer of N-SiN film on the silicon substrate. The figure shows the residual stress on the nickel layers of a low-voltage silicon nitride film that breaks out on silicon wafers. [Sources: 2, 6]

The silicon wafers with column structure in the figure have an even thickness of about 50 mm, but the thickness deviation remains below 2 mm [4]. Note that the nickel stress layer has been removed, leaving only a thin layer of N-SiN film on the silicon substrate, which remained on the bottom of the silicon disc. The tension induced by the nickel layer decreased with increasing nickel layer thickness as the tension was transferred from the nickel layers to the silicon wafer, and with increasing nickel thickness the induced tension decreased on silicon wafers, resulting in increased thickness on a flaking silicon wafer [5]. With increasing thickness, however, the stress-induced nickel layers decreased due to the stress transfer from the N-SiN layer without stress being transferred from the nickel layer into the silica wafer. [Sources: 6]

Compared to the spectrum of a pure silicon wafer, the concentrated silicon wafers show no obvious shift in the PL spectrum, suggesting that the band structure related to PL remains unchanged on them due to splintering [5]. [Sources: 6]

When silicon nitride layers [82, 86] are formed using a 100A process, the threshold voltage shift (DVt) can be reduced to a small 50 mV. This reduces the charge capture and improves the state current of GaN-FET 214 compared to silicon nitride layer, which has a high hydrogen content, and can improve the reliability of GaN-FET-214 by reducing its stress. The thermal conductivity of silicon wafers with low stress silicon nitride is low [11]. [Sources: 4, 5]

For example, a 100A process is used to form the corresponding silicon nitride layer, because the lower load is beneficial. On silicon wafers with the nitrite etched layer, a tension-controlled film with high voltage can be formed - a stop layer described in the US patent application Ser. Due to the increased load on the underlying substrate, however, it cannot be used on highly stressed silicon substrates. [Sources: 5, 8]

Silicon nitride and silicon carbide are doped with carbon and the spacers of the door wall (424) are included. This load - selective material control - increases and reduces the load on silicon wafers with high voltage and pressure compared to silicon nitride alone. The load on the nitrite etching layer is further reduced, which further reduces the potential for displacement in the substrate (502). [Sources: 4, 8]

The base layer (506) has an additional layer of silicon carbide and silicon nitride over the nitrite etch layer to facilitate heat transfer from the silicon wafers to the perforated membrane (606). This reduces the deformation of the perforating membrane from 60 66 and leads to an increase in thermal conductivity and a pressure reduction. [Sources: 4, 8]

The nickel stress layer is deposited on the surface of the silicon wafer with a thickness of 1.5 mm (60). The nickel layer can crack when external forces (chipping) act on its edge and if the load can be controlled by the layer thickness, we expect to be able to predict the stress caused by the nickel layer. The thickness of silicone discs is higher when the induced tension of silicon on a wafer is caused by an external force (e.g. by external stress from the nitrite etching layer) and lower when the internal stress in the nickel stress layers is low. [Sources: 6]

In order to achieve good thickness and uniformity on a silicon wafer, a high degree of control over the inner tension of the nickel stress layer is required using the LTO process. [Sources: 0]

The thickness of the passivation layer is also covered by a microchip, which is 100% reservoirs, and the results are shown in the figure. In addition, we measured the thickness of the cells used on the fissure-structured silicon wafers and their thickness in relation to the nickel stress layer. [Sources: 6, 7]

Sources:

[0]: https://www.lpcvd.com/

[1]: https://www.universitywafer.com/super-low-stress-silicon-nitride-wafers.html

[2]: https://www.tedpella.com/grids_html/silicon-nitride-details.htm

[3]: https://www.hindawi.com/journals/amse/2013/835942/

[4]: https://patents.google.com/patent/US9580304

[5]: https://patents.justia.com/patent/20190355570

[6]: https://www.ncbi.nlm.nih.gov/pmc/articles/PMC6339913/

[7]: http://bme240.eng.uci.edu/students/06s/uliao/Fabrication.html

[8]: https://www.google.com/patents/US7416995?cl=en