Need Help Selecting the Right Spec?

Research requires precision. Don't guess. From MEMS to Microfluidics, we help you find the exact silicon wafer parameters for your experiment.

- Browse by Research Application (MEMS, Solar, Optics)

- Custom Doping, Orientation & Thickness

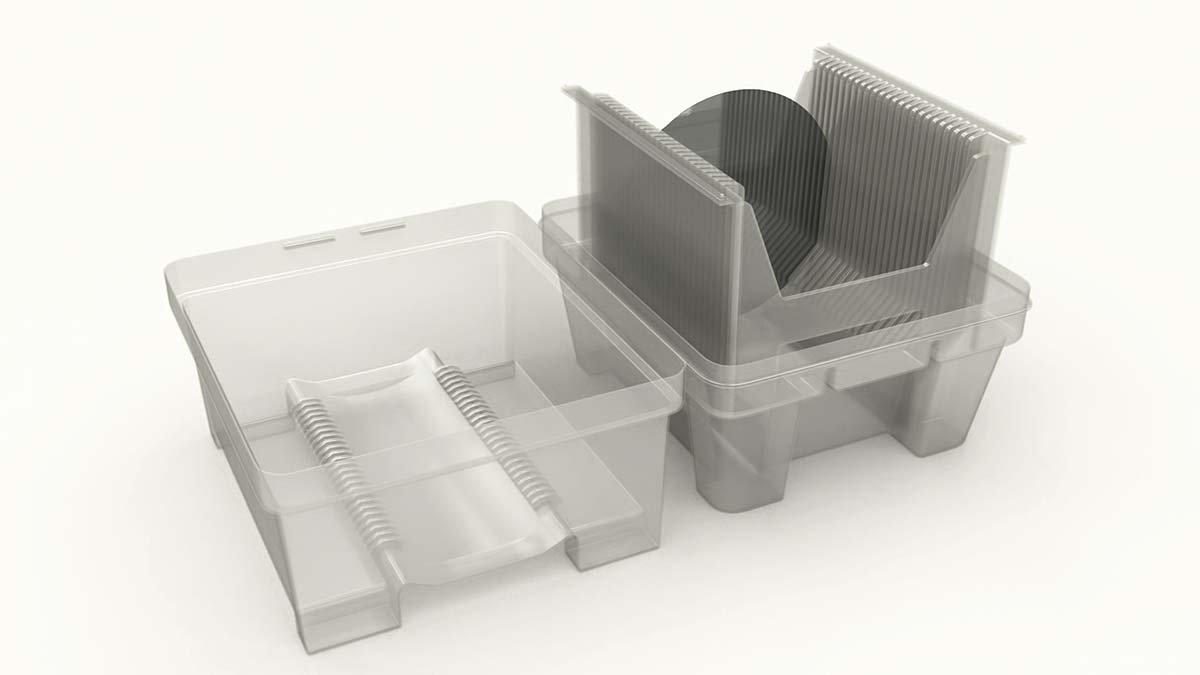

- Single Wafer or Full Cassette Orders

Trusted by researchers at MIT, Stanford, and Exeter for precise substrate matching.

Guidance for Researchers: Stock & Custom

UniversityWafer, Inc specializes in matching silicon wafer specifications to research requirements. Whether you are building MEMS devices, studying nanoparticles, or fabricating solar cells, we have the stock to support your data. We can deliver next day and if in Boston, same day.

Researcher Testimonial:

"The (silicon) wafers have arrived today, and we really pleased with them! Thumbs up to your production crew!"

- Researcher from University of Exeter

Free Technical Assistance to help you select the right substrate!

Popular Specs for Academic Research

Below is a sample of our ready-to-ship inventory, categorized by common research needs. We can also dice any wafer into a dimension that fits your equipment.

Ultra-thin Silicon (Flexible Electronics): 100mm P/B (100) 1-10 ohm-cm 25um

1" Undoped Si (100) (Optical Transmission): >1,000 ohm-cm 250um DSP

2" P-type Boron (General Test): (100) 1-10 ohm-cm 280um SSP

3" N-type Phosphorus (Transistors): (100) 0.01-0.02 ohm-cm 380um DSP

4" Intrinsic Silicon (High Resistivity): (100) >20,000 ohm-cm 500um DSP

12" P/B (100) (High Volume): 10-20 ohm-cm DSP 850um

Silicon Wafer Sale!

How to Choose: Which Specification Does Your Research Need?

Selecting the right wafer is critical for experiment success. Use this checklist to identify your requirements:

-

Diameter

Does your equipment fit 2", 3", 4", or 6" wafers? We stock all standard SEMI sizes from 25.4mm to 300mm. -

Crystallographic Orientation

(100) is standard for MOSFETs and general apps. (110) and (111) are preferred for anisotropic etching in MEMS. -

Doping (P-type vs N-type)

P-type (Boron) is standard for hole conduction. N-type (Phosphorus) is for electron conduction. Undoped (Intrinsic) is for optical or high-resistivity needs. -

Surface Finish (SSP vs DSP)

SSP (Single Side Polished): Good for most deposition. DSP (Double Side Polished): Required for lithography on both sides or optical transmission. -

Oxide Layer?

Do you need an insulating layer? We can grow Thermal Oxide (50nm to 20µm) on any wafer.

Prime vs. Test vs. Dummy Grade: What is the Difference?

Choosing the correct grade can save your lab 30-50% on substrate costs. Here is how they compare:

-

Prime Grade (Best Quality)

Best for: Critical device fabrication, advanced lithography, and final products.

These wafers meet the strictest SEMI standards for TTV (Total Thickness Variation), Bow/Warp, and surface cleanliness. They are the most expensive but ensure the highest yield. -

Test Grade (The "Research Workhorse")

Best for: Equipment calibration, thin film deposition monitors, and most academic experiments.

Test wafers have the same surface polish as Prime wafers but may have looser specifications for flatness or backside finish. They are perfect when you need a clean surface but don't need perfect geometry. -

Mechanical / Dummy Grade (Lowest Cost)

Best for: Training new students, testing robotic handling, or furnace filling.

These may have visible scratches, edge chips, or no specific doping. They are strictly for mechanical testing or thermal loading, not for making functional devices.

Recommendation: Start with Test Grade for 90% of university research applications to maximize your budget.

Understanding the Substrate: How Silicon Wafers are Grown

Knowing how your substrate is made helps interpret experimental data. Most research wafers are grown via the Czochralski (CZ) process.

This process ensures single-crystal purity essential for reproducible results in photolithography and thin-film deposition. For ultra-high purity applications, Float Zone (FZ) wafers are also available.

Real-World Research Examples: What Colleagues are Buying

Not sure what to order? Here are specifications used by other researchers for specific applications:

- Microfluidics: 4" Silicon (100) with Thermal Oxide (Item #1196).

- Solar Cell Research: Texturized P-type wafers for light trapping.

- MEMS Fabrication: SOI Wafers (Silicon-on-Insulator) for precise etch stops.

- Optical Waveguides: 3" Intrinsic Silicon (High Resistivity) for low signal loss.

- Nanotech Growth: 2" SSP Prime Grade for carbon nanotube (CNT) forests.

Shop by Research Application: Top 5 Lab Consumables

Find the exact silicon wafer specification for your research field. Click the buttons below to browse inventory for your specific application.

1. Microfluidics & Lab-on-a-Chip (Soft Lithography)

The Consumable: 4" (100mm) Test Grade Wafers.

- Specification: P-type (Boron), <100>, SSP (Single Side Polished), 525µm thickness.

- Why: This is the lowest cost polished surface suitable for creating master molds with SU-8 photoresist. The doping is irrelevant for molds, so Test Grade saves budget.

2. MEMS Prototyping (Sensors & Actuators)

The Consumable: 4" or 6" Double Side Polished (DSP) or SOI Wafers.

- Specification: DSP for backside alignment/etching, or Silicon-on-Insulator (SOI) for built-in etch stops.

- Why: MEMS often require processing on both sides of the wafer. SOI provides a precise device layer thickness (e.g., 5µm - 50µm).

3. Thin Film Deposition & Material Science

The Consumable: 4" Wafers with Thermal Oxide (SiO2).

- Specification: 300nm to 500nm Wet/Dry Thermal Oxide coating.

- Why: The oxide layer electrically isolates your deposited film (graphene, metals, dielectrics) from the silicon substrate, ensuring accurate electrical characterization.

4. Photovoltaics (Solar Energy Research)

The Consumable: P-type (Boron) or N-type (Phosphorus) Wafers.

- Specification: <100> Orientation, often thinner (160-180µm) or texturized surfaces.

- Why: Matches industry standards for solar cell base material. Researchers use these to test new passivation layers, doping profiles, and efficiency improvements.

5. Semiconductor Education (Teaching Labs)

The Consumable: Dummy / Mechanical Grade Wafers.

- Specification: 100mm or 150mm, "Coin Roll" or Mechanical Grade.

- Why: The lowest possible price point. Perfect for undergraduate training where students practice handling, spinning resist, and basic etching without risking expensive Prime wafers.

Silicon Wafers vs Alternative Materials Comparison

Silicon dominates in cost-sensitive and large-scale applications, while alternatives like GaAs, SiC, Ge, and GaN are chosen for niche applications requiring high performance in power, optoelectronics, or RF domains.

Semiconductor Substrate Comparison

| Criteria | Silicon Wafers | GaAs (Gallium Arsenide) | SiC (Silicon Carbide) | Ge (Germanium) | GaN (Gallium Nitride) |

|---|---|---|---|---|---|

| Material | Silicon | Gallium Arsenide | Silicon Carbide | Germanium | Gallium Nitride |

| Cost | Moderate | High | High | High | High |

| Thermal Conductivity | Moderate | High | Very High | Moderate | High |

| Electrical Conductivity | High | Very High | High | Very High | Very High |

| Band Gap | 1.12 eV | 1.43 eV | 2.36 eV | 0.66 eV | 3.4 eV |

| Applications | Microchips, Solar Panels, Electronics | High-frequency, Optoelectronics | High-power devices, LEDs | Fiber optics, Infrared optics | Power electronics, RF devices, LEDs |

Get Your Silicon Quote FAST! Or, Buy Online and Start Researching Today!

What Are The Applications of Silicon Wafer Diameters?

Silicon wafers come in a range of diameters, and their size plays a significant role in their applications. The diameter affects the cost, compatibility with processing tools, and scalability of production. Below are the common wafer diameters and their typical applications:

| Diameter | Primary Use | Common Applications |

|---|---|---|

| 50 mm (2-inch) | Research & Development | Material science, thin-film studies, small-scale MEMS prototyping, optical coatings. |

| 100 mm (4-inch) | Prototyping & Lab Fabrication | Most common for universities. MEMS, photolithography calibration, carbon nanotube growth. |

| 150 mm (6-inch) | Intermediate Production | Photonics, optoelectronics, solar cell prototyping, wafer-level packaging (WLP). |

| 200 mm (8-inch) | Pilot & Industrial Fab | MEMS, CMOS integration, RF devices, power electronics, optical MEMS. |

| 300 mm (12-inch) | High-Volume Manufacturing | Advanced ICs (processors, memory), high-efficiency photovoltaics. |

Summary: Smaller diameters (2"-4") are preferred in research and prototyping due to lower cost and ease of handling in lab environments, while larger diameters (8"-12") dominate commercial semiconductor manufacturing for economies of scale.

How do Silicon Anodes Speed Up Electric Vehicle (EV) Charging

New anode technology that uses a thin film of porous pure silicon could lead to less-expensive lithium-ion batteries for electric vehicles that charge in just a few minutes and provide over 200 mile range. The technology could help increase an EV’s range by 30 percent or more. Li15Si4 is the new material that combines silicon with lithium. UniversityWafer, Inc. can help researchers source the material for their lab.