Hi, I am looking for a semiconducting Gallium Arsenide wafer without intentionally doping. Carrier density lower than 10^16 cm^-3 is preferred, if not,<10^18 cm^-3 is also acceptable. Please note that I don't need deep level dopants to make the wafer Semi-Insulating! Other properties are quite flexible.

What is The Carrier Density Of My Substrate?

GaAs Wafers With Low Carrier Density

A PhD candidate requested a quote for the following.

Reference #137380 for specs and pricing.

Get Your Quote FAST! Or, Buy Online and Start Researching Today!

GaSb Carrier Density At Room Temperature

A group leader in a physics department requested help with their Gallium Antimonide subtrate order.

I can use the Gallium Antimonide wafers if the carrier density is indeed measured at 300 K.

Question:

So can you let me know if the carrier densisty is measured at room temperature?

Answer:

Yes, the items we quoted below can meet the specs you required and the carrier density is indeed measured at room temperature (300K).

Item Qty. Description

CS33c. 10(MOQ) Gallium Antimonide wafers, P/P 2"Ø×400±25µm,

p-type GaSb:-[110]±0.5°,

Nc=(1E16-2E16)/cc,

Both-sides-polished, US Flats,

Sealed under nitrogen in single wafer cassette.

NOTE: Nc and Mobility are at 300ºK.

CS33d. 5(MOQ) Gallium Antimonide wafers, P/P 30mm-40mm Ø×400±25µm,

p-type GaSb:-[110]±0.5°,

Nc=(1E16-2E16)/cc,

Both-sides-polished, US Flats,

Sealed under nitrogen in single wafer cassette.

NOTE: Nc and Mobility are at 300ºK.

Reference #154906 for specs and pricing.

(Charge Carrier Density) by van der Pauw's Method

A postdoc requested a quote for the following.

Please give me a quote for Si wafer, 1" diameter, 100 Orientation, one-side polished, with Ori mark at the side. Doping, resistivity are unimportant (they will be used for metal evaporation experiment). A pack of 15-25 would be fine.

Question:

What does Ori mark meaning flat?

Answer:

For "Ori mark", I mean that the side of the round-shaped wafer is usually cut along a crytallographic direction at the side for indicating a crystal axis. Since we have to cut them after processing, this makes our life easy, and we do not need to orient each crysral individually. See image below.

The documentation constituting the Certificate of Conformance for EB96 will include:

- Electrical parameters (Charge carrier density) by van der Pauw's method for each of the thicker layers.

- Measurement of the GaAs(1-x)P(x) by Photoluminescence and X-Ray DIffraction for the test layer.

- Photoluminescence map for the entire wafer.

- Optionally, we can do a SEM {rather than TEM} picture showing the thickness of each layer. However that is a destructive test. So either the client will pay for a second wafers or the client will section his wafer and send us back a sliver on which we can do the SEM scan.

- Optionally, we can do a TEM picture. However, we have access to a SEM for free, but we would have to buy time on a TEM. That would cost about $ . Again, like with SEM, this is a destructive test, so either the client will pay for a second wafers or the client will section his wafer and send us back a sliver on which we can do the TEM picture.

Reference #204586 for specs and pricing.

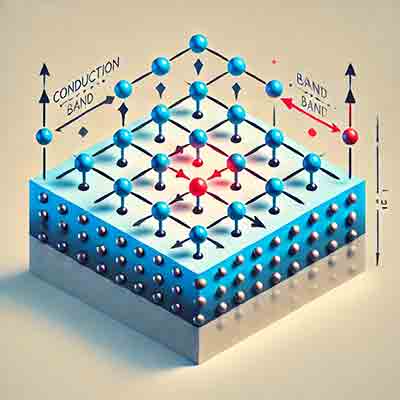

What is Carrier Density?

Carrier density in semiconductors refers to the concentration of free charge carriers—electrons and holes—in the material. These charge carriers are responsible for electrical conduction. Carrier density is typically expressed as the number of carriers per unit volume, usually in cm−3.

Here's a quick breakdown:

-

Electrons (n): In n-type semiconductors, electrons are the majority carriers. The electron density (or

concentration) is denoted by .

concentration) is denoted by . -

Holes (p): In p-type semiconductors, holes are the majority carriers. The hole density (or concentration) is denoted by .

-

Intrinsic Carrier Density: In an intrinsic (pure) semiconductor, the carrier density is denoted by ni, which is the concentration of electrons or holes in a pure material with no added impurities. In an intrinsic semiconductor, n=pni.

Carrier density can vary widely based on the type and level of doping (addition of impurity atoms), temperature, and the material’s intrinsic properties. Doping increases the carrier density in a controlled way to improve the semiconductor's conductivity.

Why Do You Need to Know The Carrier Density of a Silicon Wafer?

Knowing the carrier density of a silicon wafer is crucial for controlling and predicting its electrical properties, which directly impacts its performance in electronic devices. Here are several reasons why understanding carrier density is essential:

-

Device Performance: The carrier density determines the conductivity of the silicon wafer. Higher carrier densities typically mean better conductivity, which is essential for optimizing device performance, whether it's a transistor, diode, or sensor.

-

Junction Formation: When creating p-n junctions, such as those in transistors, the carrier densities on each side of the junction control how the junction behaves. For instance, it influences parameters like the depletion width and the built-in potential, which are fundamental for the device's switching properties.

-

Precision in Doping: In semiconductor manufacturing, specific carrier densities are achieved through precise doping (adding impurities). Accurate knowledge of carrier density ensures that the wafer has the desired electrical characteristics, which are critical for creating consistent, reliable devices.

-

Thermal and Optical Properties: Carrier density affects the thermal and optical properties of silicon, which is especially relevant in optoelectronic devices and sensors. For instance, in photodetectors or solar cells, the carrier density influences the material's response to light.

-

Design and Simulation: Understanding the carrier density allows engineers to simulate device behavior more accurately. This helps in designing circuits and predicting how the silicon wafer will perform under different conditions, such as varying voltages, temperatures, or frequencies.

-

Control of Leakage Current: Excessive carrier density can lead to high leakage currents in devices. Accurate knowledge of carrier density allows for control over leakage currents, which is especially important in low-power applications.

For applications involving light interaction, such as your daughter’s project measuring conductivity under light exposure, knowing the intrinsic carrier density can help predict the baseline conductivity of the wafer and how it will change when illuminated.

What Is Free Carrier Density?

Free carrier density refers to the concentration of charge carriers—electrons in the conduction band and holes in the valence band—that are free to move within a semiconductor material and participate in electrical conduction. Unlike bound carriers, which are tightly associated with atoms or defects, free carriers are mobile and can respond to electric fields, enabling current flow.

In more detail:

-

Electrons and Holes:

- Electrons are negatively charged carriers that occupy the conduction band. In n-type materials, these are the majority carriers.

- Holes are effectively positively charged carriers in the valence band. They represent the absence of an electron in the atomic lattice and are the primary carriers in p-type materials.

-

Relation to Temperature and Doping:

- At higher temperatures, more electrons can gain enough energy to jump from the valence band to the conduction band, generating electron-hole pairs and increasing the free carrier density.

- In doped semiconductors, doping introduces impurities that donate free electrons (in n-type materials) or accept electrons to create holes (in p-type materials), significantly increasing the free carrier density beyond the intrinsic level.

-

Measurement and Units:

- Free carrier density is typically measured in terms of the number of carriers per unit volume, such as .

- In an intrinsic (undoped) semiconductor, the free carrier density is represented by ni , the intrinsic carrier concentration, and is equal to the number of electrons or holes in the absence of doping.

-

Importance in Device Behavior:

- The free carrier density dictates the semiconductor's conductivity, which is directly proportional to the carrier density and the mobility of those carriers.

- It affects the performance characteristics of devices, including response times, power efficiency, and switching speed.

For example, in silicon at room temperature, the intrinsic carrier density (ni) is about 1.5×1010cm-3. Doping can increase the carrier density to orders of magnitude higher, depending on the desired application and electrical properties of the device.

What is Graphene Carrier Density?

A PhD student requested help with the following.

Question:

I have a number of queries:

- How large are the monolayers? Can you show a sample image?

- Whats the method you use to grow or is it exfoliated? In each can you please explain the process a bit (e.g. dry transfer/ wet transfer/ stamping etc.)

- Do you have an idea regarding the carrier density and mobility in your graphene samples?

We are interested in monolayer/ bilayer Graphene on substrates/ films provided by us. However, since its for a specific purpose we are very much particular about the quality.

Btw, one more query: do you grow other 2D materials (TMDC, BP) as well? Some of the people in our

Answer:

Our graphene's carrier density is in the order of 3x10E13cm-2.

- The current minimum size we can grow is 3 diameter wafer and the large size 4 diameter wafer or 70 mm x 70 mm.

- The growth method we use is the Chemical Vapor Deposition process (CVD), and after we use a wet transfer.

- FET Electron Mobility on Al2O3: 2000 cm2/Vs and FET Electron Mobility on SiO2/Si: 4000 cm2/Vs

We do not grow other materials apart from graphene. - We can transfer graphene monolayer and bilayer on to your customer`s substrate. for making a quote we need to know the size he wants.

- We would be grateful if your customer could complete the enclosed questionnaire, in order to ensure if we can transfer graphene on to his substrates.

Reference #214522 for specs and pricing.

Low Carrier Density for Silicon-on-Insulator (SOI) Wafers

An assistant professor requested a quote for the following substrate.

I actually need some supplies for SOI wafers but not the one from the list. Particularly, I need Part No. 534001 (dia 150mm, handle thick 400 micron, handle res 1-20 Ohmcm, buried oxide 20000 A, device thick 5 micron, device res >150 Ohmcm, handle type N, device type Any). Do I understand correctly that you can provide this wafer with any doping I need? For my application, the carrier density should be as low as possible so intrinsic would be ideal but low p- or n-type doping is fine as well. Can you please send a quotation with three of these wafers? Whats the price and current lead time? Also, is there a discount if buying even more?

I need SOI wafers with device thickness of 4-5 micron and buried oxide thickness >= 1 micron. Unfortunately, there is no wafer on the list you sent over which fits to these requirements.

Reference # 248827 for specs and quantity.